The Design Truth About ARM

Fully linear power supply: In the choice between ARM and X86 platforms, there is a common misconception that ARM is power-efficient and thus easier to design with linear power supplies, while X86 is power-hungry and difficult to design with linear power supplies.

Actually, a watershed emerged around the release of dual-core ARM chips. Some ARM manufacturers began to bundle PMICs (power management integrated circuits) with ARM chips during sales, where the PMIC uniformly handles the power supply and power-up sequencing for various voltages of the ARM. A key concept here is power-up sequencing—meaning that voltage A must be powered on X ms earlier than voltage B, and voltage B must be powered on Y ms earlier than voltage C. For example, the 1.5V memory operating voltage must be switched on at least 100ms before the 0.9V CPU operating voltage; otherwise, the CPU will fail to boot due to undetected memory. As ARM chips incorporate not only memory but also numerous functional modules like external storage, ADC, and DAC—each with distinct power-up timing requirements—managing their power-up sequences has become extremely complex. This complexity has increased alongside the growth in the number of ARM CPU cores, interfaces, and interface types. Since only ARM original manufacturers fully understand the power-up sequences of their own ARM chips, they introduced PMICs for bundle sales to reduce development difficulties for design partners and enhance profits. The emergence of PMICs perfectly addresses the challenge of extremely complex power-up sequencing, making the use of PMIC chips from ARM original manufacturers almost the only option for product design.

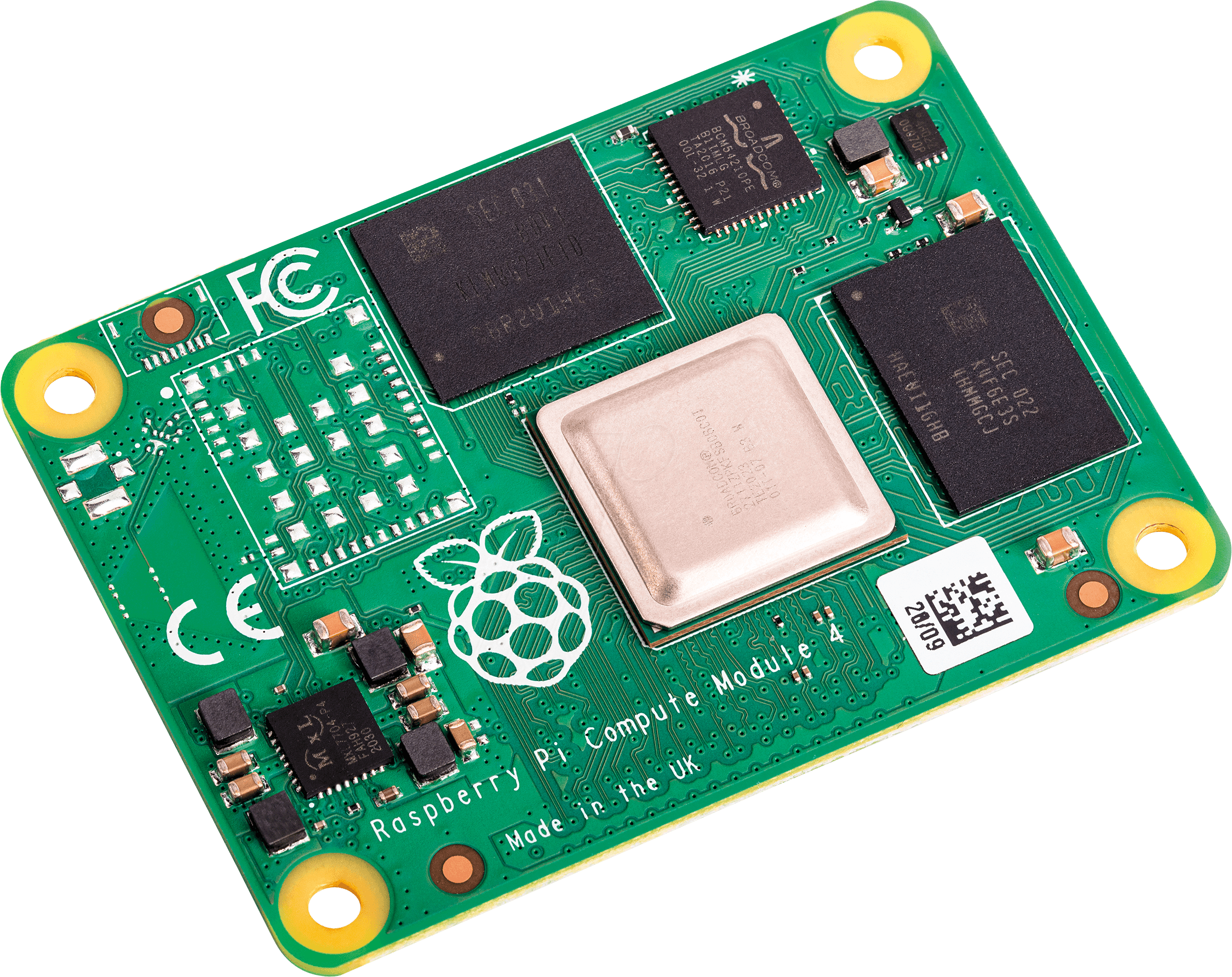

With the increase in the number of ARM cores and the improvement of performance, the required operating current has also been increasing. Starting from quad-core ARM, switching power supplies have been used for CPU power supply to address the contradiction between the increased CPU power supply current and the surge in heat dissipation caused by the growth in the number of cores. Currently, industry-standard solutions use switching power supplies built into PMICs (power management integrated circuits) to power the CPU, memory, and numerous circuits that significantly affect sound quality. As a result, ARM chips with PMICs used in quad-core and higher configurations have almost no possibility of being designed with full linear power supplies. Although there are still a few linear power supplies inside the PMIC, these have minimal impact on HiFi design.

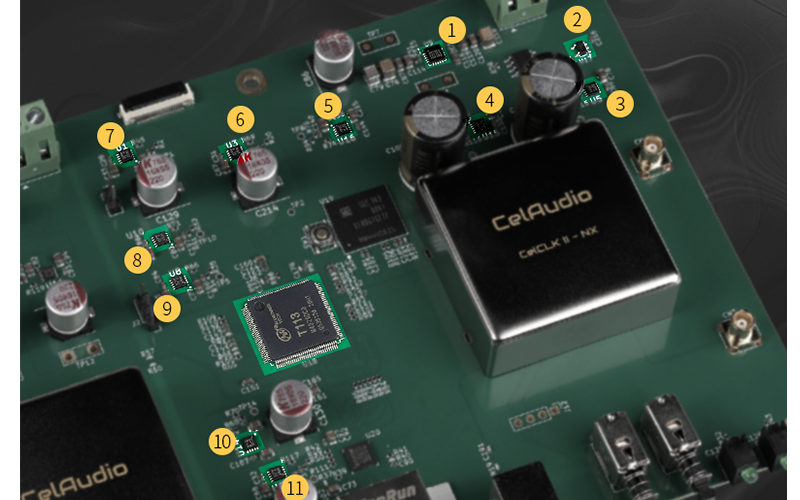

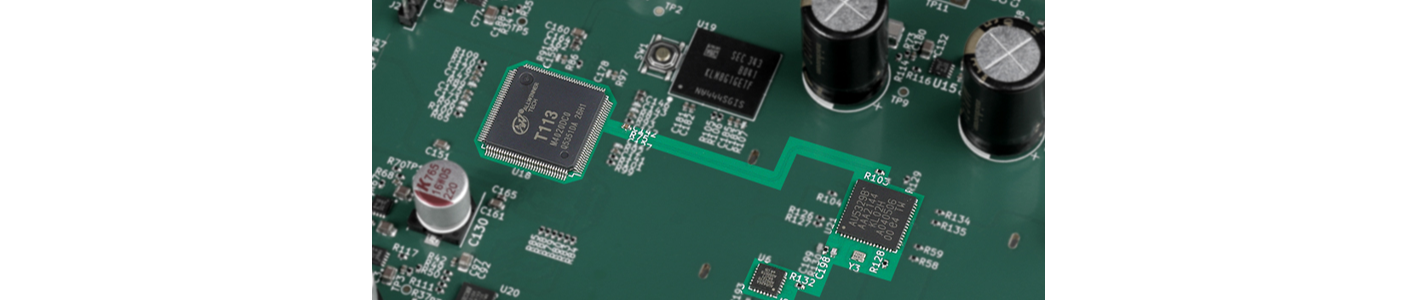

CelAudio utilizes the T113-S4 dual-core ARM and employs up to 11 LDOs in the entire circuit, completely separating the power supply circuits for the CPU, clock, memory, external storage, I/O, and network. Through a self- developed solution, it achieves full control over the power-up sequencing of the T113-S4, ensuring the operational stability of the hardware system. This enables the realization of a stable, low-interference fully linear power supply design for the A1 platform.

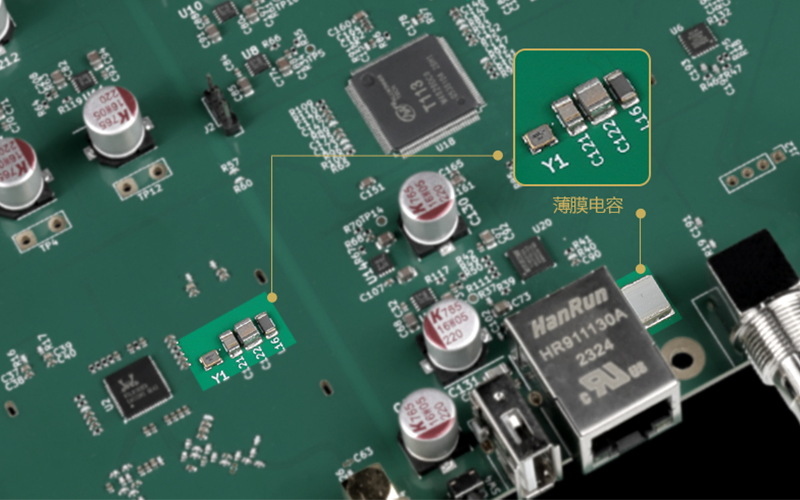

Clock: To simplify the complexity of power-up sequencing, ARM designs typically use passive crystals that can be directly controlled by the ARM. As is well known, the quality of clock signals is a critical factor affecting sound quality in digital audio playback and HiFi network devices. High-quality, common-source clocks can set a higher ceiling for sound quality. Therefore, replacing passive crystals with high-quality, common-source clocks is undoubtedly a superior solution. In the design of the A1 architecture, CelAudio replaces passive crystals with the CelCLK II PLL system, providing common-source clocks for the CPU, network, and other systems. Meanwhile, it overcomes the issue of geometrically increased power-up timing complexity caused by this change, enabling the A1 architecture to feature a native high-quality common-source clock system.