ARM的设计真相

全线性供电: 在ARM平台和X86平台的选择中,很容易产生一个误区,就是ARM省电,所以更容易设计成线性供电,而X86费电不容易设计成线性供电。

实际上大约在双核心ARM发布时候开始出现一个分水岭,部分ARM厂家在销售ARM时会捆绑销售PMIC,由PMIC统一负责ARM的各个电压的供电和上电时序。这里有一个关键的概念——上电时序,那么什么是上电时序?上电时序就是A电压必须比B电压早X ms上电,而B电压要比C电压早Y ms上电。举个例子,内存工作电压1.5V 必须比CPU工作电压 0.9V早至少100ms开启电源开关供电(上电),否则CPU就会因为没有检测到内存而启动失败。由于ARM不仅有内存,还有外存、ADC、DAC等大量功能模块,而不同功能模块有不同的上电时序要求,这让ARM的上电时序管理变得极其复杂。伴随ARM CPU核心数量、接口数量和接口种类的增加,这个上电时序就越来越复杂。由于只有ARM原厂商才最为清楚自己ARM的上电时序,为了降低ARM设计合作伙伴的开发难度,也为了提升自身的利润,各ARM厂家均推出了PMIC捆绑ARM销售。PMIC的出现,完美的解决了上电时序极度复杂的困难,而采用ARM原厂商的PMIC芯片进行产品设计也几乎成为唯一选择。

伴随ARM核心数量的增加,性能的提升,需要的工作电流也越来越大。从四核心ARM开始,CPU供电均采用开关电源以解决核心数量增长带来的CPU供电电流增加与发热量激增的矛盾。目前行业内的解决方案,均通过PMIC内置的开关电源为CPU、内存以及大量对声音产生重大影响的电路供电。因此4核心以后,使用PMIC的ARM几乎不会有设计成为全线性供电的可能性。当然PMIC内部仍存在少量线性电源,但是这些线性电源对HiFi设计影响甚微。

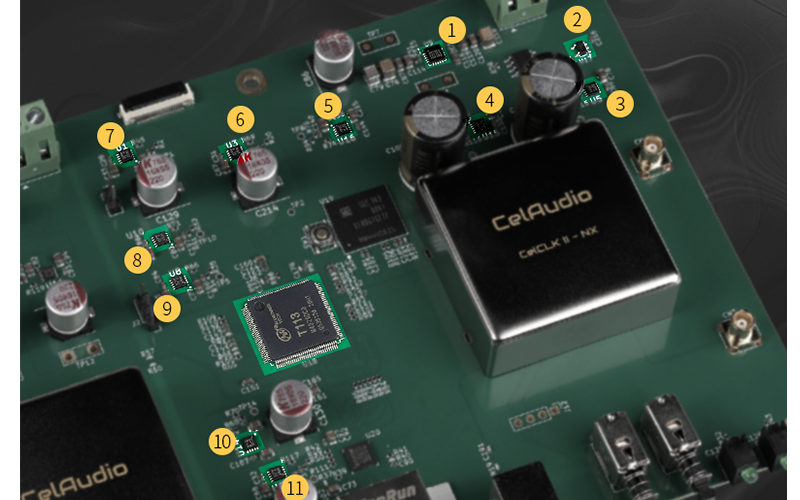

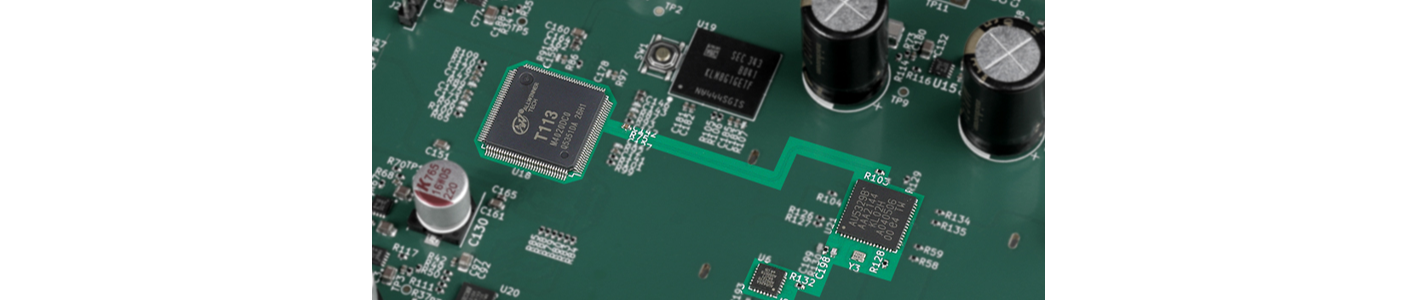

赛耳之声使用T113-S4双核心ARM,整个电路采用高达11颗LDO,将CPU、时钟、内存、外存、I/O和网络等供电电路完全分立,进而通过自行设计的方案,实现了对T113-S4上电时序的完全控制,确保了硬件系统的运行稳定性,从而完成了稳定、低干扰的A1平台全线性供电设计。

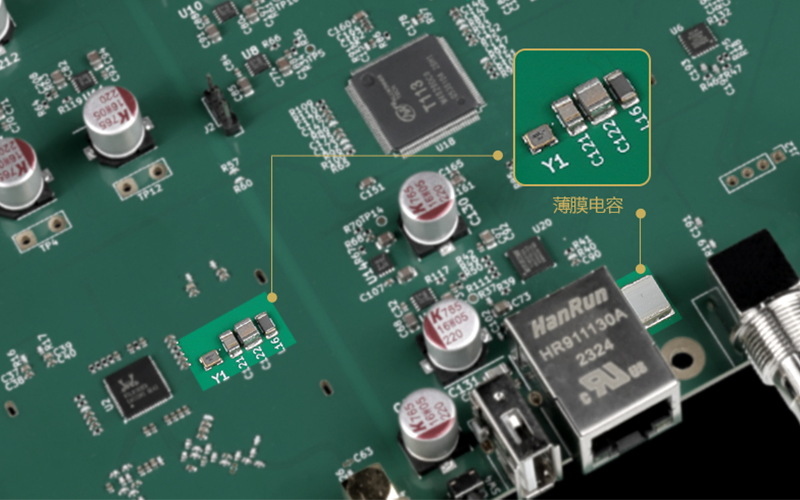

时钟: 为了简化上电时序的设计难度,ARM设计中通常使用可以被ARM直接控制的无源晶体。众所周知,时钟信号质量是影响数字播放和HiFi网络设备声音质量的关键要素,高质量、同源时钟可以提供更高的声音质量上限。因此使用高质量、同源时钟代替无源晶体,无疑是更加优秀的解决方案。赛耳之声在A1架构的设计中,使用CelCLK II PLL系统取代了无源晶体,对CPU、网络等系统提供了同源时钟,并且克服了由此引发的上电时序复杂度几何级提升的问题,从而使A1架构拥有了一个原生的高质量、同源时钟系统。